Solution Guides Technical Support Using PI Simulation

Recently, with enhancements of functionality and performance of electronic systems, the consumption current of ICs has been increasing. On the other hand, with the miniaturization of the internal structure of ICs due to increased functionality, its withstand voltage and power-supply voltage have decreased. With the decrease in the withstand voltage and power-supply voltage, it is becoming important to reduce voltage fluctuations. Therefore, the impedance [Z] needs to be reduced further to suppress voltage fluctuation.This guide introduces our technical support using Power Integrity (PI) simulations aimed at reducing the impedance of power-supply lines and the quantity of decoupling capacitors necessary through the replacement of two-terminal Multi Layer Ceramic Capacitors (MLCCs) with low-ESL capacitors.

Contents

Reducing impedance and decreasing the quantity of decoupling capacitors are needed further

With a decrease in power-supply voltage value, it is becoming more important to reduce the impedance of power-supply lines.

The impedance of decoupling capacitors needs to be reduced in order to moderate voltage fluctuations. This guide introduces about number reduction in decoupling capacitors by replacement on low ESL capacitors to achieve such as the board size and the impedance characteristic which are asked in the severe restriction.

Decoupling capacitors for low-voltage/high-current power-supply lines

With the recent increase in the functionality and operation speed of electronic systems, Power Integrity (PI) of power-supply lines for digital ICs in the system is becoming important.

In order to enhance PI, it is important to reduce the impedance of the power-supply line as much as possible. For that reason, a lot of MLCCs are used in the power-supply line as decoupling capacitors.

However, with set miniaturization, restrictions on board size and mounting area are becoming tighter, and it is becoming difficult to mount the large number of MLCCs required to realize the desired impedance characteristics.

Impedance can be reduced by mounting multiple capacitors side by side.

Currently, large quantities of decoupling capacitors are usedIssues: Large required quantities of capacitors, restricted mounting areas, increased costs (mounting costs)

Low impedance can be realized by fewer composition of Low-ESL capacitors

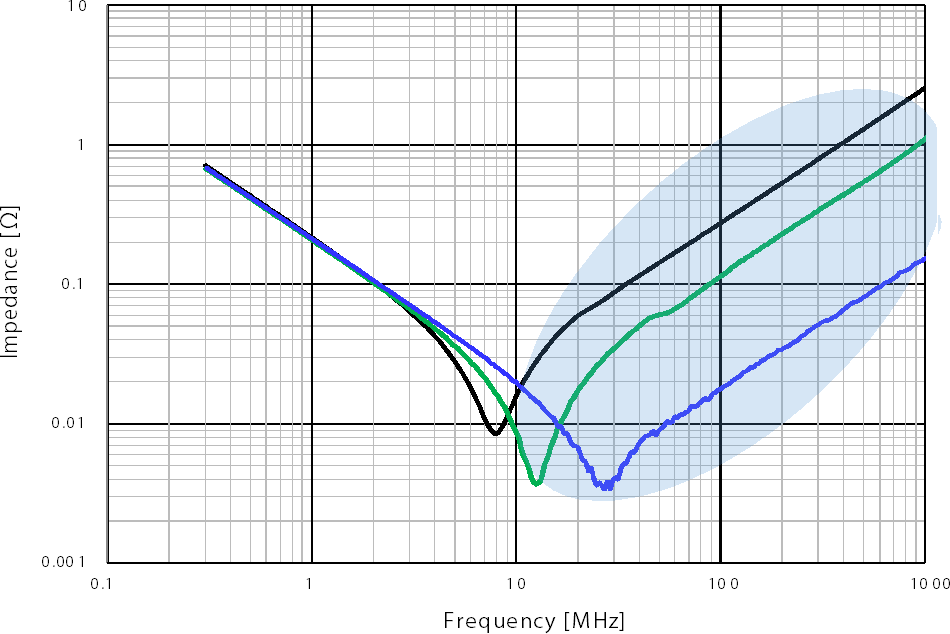

TDK recommends using low ESL-type capacitors to reduce the quantity of decoupling capacitors and total mounting area necessary. Low ESL-type capacitors themselves have a small inductance element (ESL) and realize low impedance over a broad range, including at high frequencies. Therefore, fewer low ESL-type capacitors are required to realize the impedance characteristics realized by using multiple normal-type capacitors.

2-Temination typeESL:approx. 200~300pH (1005 size)

Low ESL type (Flip type)ESL:approx. 60~100pH (0510 size)

Low ESL type (3-Temination type)ESL:approx. 20~30pH (1005 size)

Low impedance can be realized by fewer composition of Low-ESL capacitors

2-Termination type0.1μF_1005 sizex10pcs.

3-Termination type1μF_1608 sizex1pc.

or

Flip type1μF_0510 sizex2pcs.

Realizing low impedance with fewer low ESL capacitors

Also the board wiring patterns are part of electric circuits

In order to realize low impedance power-supply lines, not only are the optimum selection and configuration of decoupling capacitors important, but so is the design of the mounting board pattern. In mounting boards, resistance elements, parasitic inductance, and floating capacitance are present on the wiring conductor pattern and Via. Therefore, regarding the design of power-supply line impedance, the electrical elements of the board itself need to be included as impedance elements when designing the board pattern.

TDK can offer power-supply line impedance simulations which include board information

Power-supply design support using PI simulation

TDK provides technical support for designing optimum power-supply lines through verification based on PI simulations that incorporate mounting board information. Depending on the mounting board configuration, such as board type, mounting surface, and layouts of IC pins and peripheral parts, we propose optimum capacitor types, quantity and configuration, board wiring pattern, and layout, etc.

Generally, the number of various restrictions increases through the course of board designing. Therefore, this support can be utilized most effectively at the time of initial verification, before designing the board pattern.

Even before launching fully into the design of board patterns, we may be able to perform verifications and make proposals regarding the number of MLCCs required as decoupling capacitors, and the allowable distance in cases where MLCCs cannot be placed near ICs. Therefore, please consult with us as early in the development stage as possible if you have any problem with power-supply line design.

Please note in advance that some information needs to be provided in order to use this support service.

Download document

Please make use of this document in the increasingly severe field of impedance optimized power-supply line design, and in applications for decoupling capacitor compositions and board design techniques, which are continuing to grow in importance.

Contents of document

- Vol.1 Reducing impedance to moderate voltage fluctuation

- 1-1 With a decrease in power-supply voltage value, it is becoming more important to reduce the impedance of power-supply lines

- 1-2 Impedance reduction approach in decoupling capacitors

- 1-3 A reduction in the quantity of decoupling capacitors necessary through replacement with low-ESL capacitors

- Vol.2 Proposing reduced impedance and quantity of decoupling capacitors necessary through PI simulation

- 2-1 With an increase in the functionality of ICs, Power Integrity (PI) is becoming more important

- 2-2 PI simulation: A simulation method including not only electronic components but also board elements

- 2-3 Using PI simulation to propose optimum decoupling capacitors and board design