ソリューションガイド PIシミュレーションを活用した技術サポート

昨今、各電子システムの高機能、高性能化に伴い、ICの消費電力量は益々高まっています。また、ICの高機能化により内部構造の微細化が進むことで、ICの耐電圧が下がり、電源電圧値は低下しています。その低下に伴い、電圧変動を小さく抑えることが必要になっている一方、IC消費電流変化は増加しています。そのため、電圧変動の抑制にはインピーダンスのさらなる低減が重要になっています。

本記事では、PI(パワーインテグリティ)シミュレーションを活用した、2端子MLCC(積層セラミックチップコンデンサ)から低ESL品への置換による、電源ラインのインピーダンス低減およびデカップリングコンデンサの員数低減を目的とした技術サポートについてご紹介します。

目次

いっそう求められるインピーダンス低減とデカップリングコンデンサの員数削減

電源電圧値の低下により、電源ラインのインピーダンス低減がいっそう重要になっています。

電圧変動の抑制には、デカップリングコンデンサのインピーダンス低減が必要です。基板サイズや実装エリア等の厳しい制限の中で求められるインピーダンス特性を実現するために、TDKが提案する低ESL品への置換によるデカップリングコンデンサの員数削減についてご紹介します。

低電圧/大電流電源ラインのデカップリングコンデンサ

電子機器システムの高機能化、高速動作化に伴い、システム内部のデジタルIC用の電源ラインの特性(PI:パワーインテグリティ)が重要になってきています。PIを向上させるには、電源ラインのインピーダンスを低く抑えることが重要で、そのため、電源ラインには多数のMLCCがデカップリングコンデンサとして使用されています。

しかし、セットの小型化に伴い、基板サイズや実装エリアの制限はいっそう厳しくなっており、所望のインピーダンス特性を得るために必要なMLCC の多数実装が難しくなってきているのが現状です。

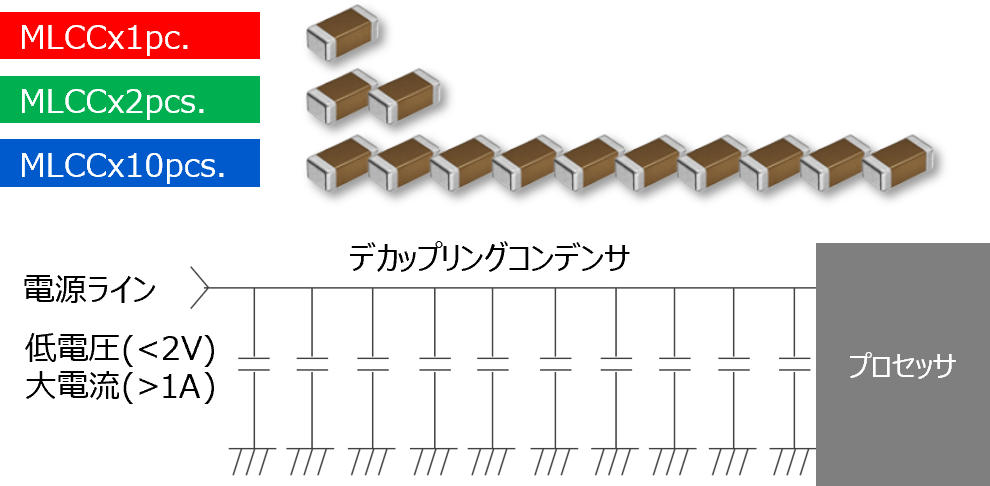

コンデンサを複数個並べることで低インピーダンス化が可能。

デカップリングコンデンサが多数使われているのが現状課題:員数多い 実装面積に余裕がない コスト増(実装費)

少ない員数構成で低インピーダンス化できる低ESLコンデンサ

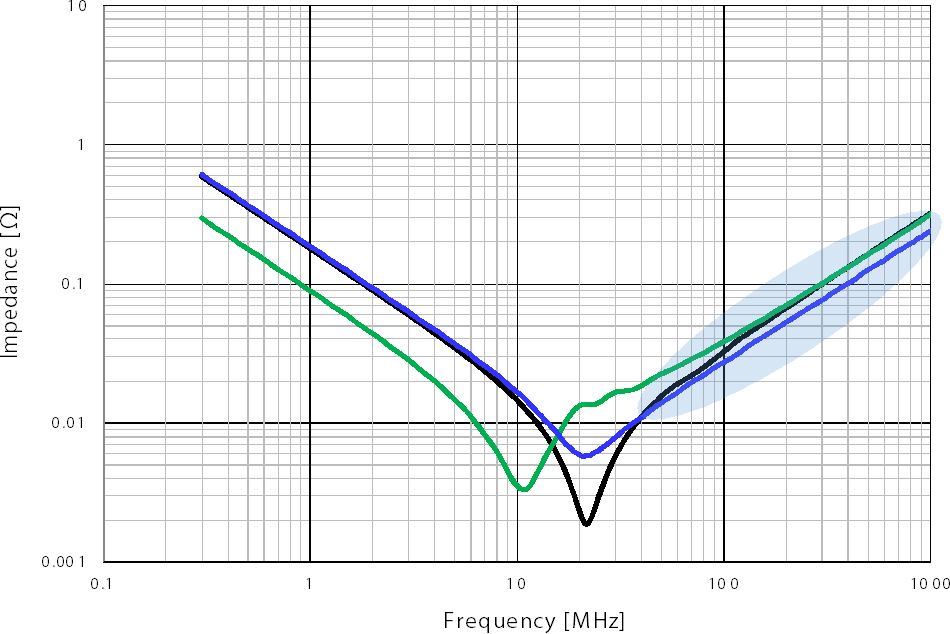

そこで、TDKでは低ESLタイプのコンデンサによるデカップリングコンデンサの員数低減、実装面積低減を推奨しています。低ESLタイプのコンデンサはそれ自身のインダクタンス成分(ESL)が小さい製品で、高周波領域まで広帯域に低インピーダンスを実現しています。そのため、通常タイプのコンデンサを複数個使って実現しているインピーダンス特性を、低ESLタイプのコンデンサはより少ない個数で実現します。

2-Temination typeESL:approx. 200~300pH (1005 size)

Low ESL type (Flip type)ESL:approx. 60~100pH (0510 size)

Low ESL type (3-Temination type)ESL:approx. 20~30pH (1005 size)

少数の低ESL品で低インピーダンスを実現

2-Termination type0.1μF_1005 sizex10pcs.

3-Termination type1μF_1608 sizex1pc.

or

Flip type1μF_0510 sizex2pcs.

少数の低ESL品で低インピーダンスを実現

基板配線パターンも電気回路の一部

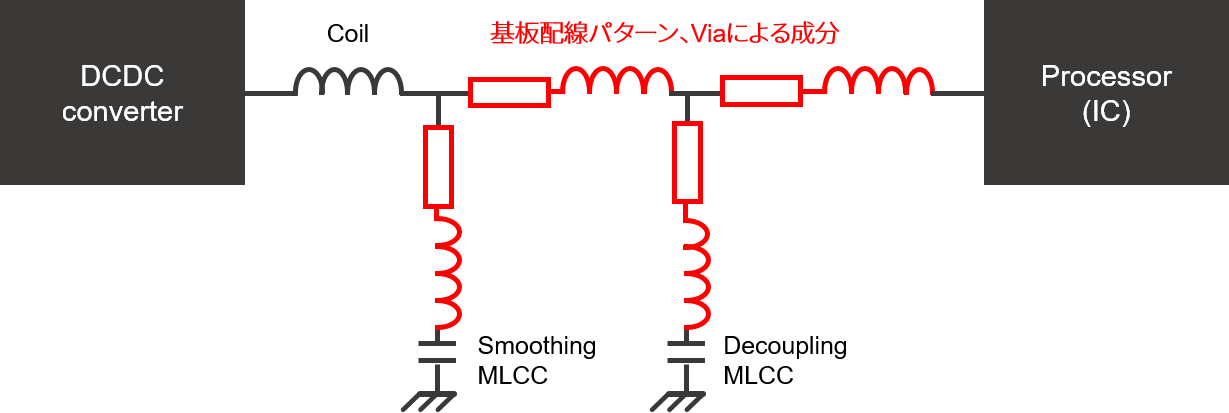

また、電源ラインの低インピーダンス化にあたっては、デカップリングコンデンサの最適選定、最適構成化のみならず、実装基板のパターン設計も重要です。実装基板において、配線用の導体パターンやViaには、抵抗成分や寄生インダクタンス、浮遊容量が存在するため、電源ラインのインピーダンス設計においては、基板自身の電気的成分もインピーダンス成分の一部と加味して、基板パターン設計する必要があります。

TDKは基板情報を含む電源ラインインピーダンスシミュレーションが可能です。

PIシミュレーションを用いた電源設計サポート

TDKでは実装基板情報を取り入れたPIシミュレーションによる検証で、最適な電源ライン設計の技術サポートを行っています。基板タイプ/実装面/ICピンレイアウト/周辺部品のレイアウトなど、実装基板の構成に応じて、最適なコンデンサタイプの選定、員数構成、基板配線パターン、部品レイアウト等のご提案を行います。

一般的に基板設計が進むにつれ各種制約が増えるため、本サポートをお客様の開発に十分に反映するためには、基板パターン設計前の初期検証時が最も有効活用できるタイミングとなります。

例えば、デカップリングコンデンサとして必要となるMLCC 数や、MLCC をIC 近辺に配置できない時の許容距離など、基板パターン設計を本格的に開始する前でも検証、ご提案できることもありますので、電源ライン設計にお困りの際は、出来るだけ開発の早い段階でご相談ください。

なお、本サポートをご利用の際にご提供いただくことが必要となる情報がございますので、予めご了承願います。

資料をダウンロードする

※よりシビアになる電源ラインのインピーダンス最適化設計、より重要性が高まるデカップリングコンデンサ構成や基板設計にぜひお役立てください。

資料掲載内容

- Vol.1 インピーダンス低減で、電圧変動を抑える

- 1-1 電源電圧値の低下により、電源ラインのインピーダンス低減がいっそう重要になっています。

- 1-2 デカップリングコンデンサにおける インピーダンス低減アプローチ

- 1-3 低ESL 品への置換によるデカップリングコンデンサの 員数削減

- Vol.2 PI シミュレーションで、インピーダンス低減とデカップリングコンデンサの員数削減をご提案

- 2-1 IC の高機能化により、PI(パワーインテグリティ)が いっそう重要になっています。

- 2-2 PI シミュレーションとは:電子部品のみではない基板成分も含むシミュレーション法

- 2-3 技術サポート対応中:PI シミュレーションを活用した最適なデカップリング コンデンサ構成および基板設計をご提案