Q.

About the J-STD-020 Reflow profile

- Capacitors >

- Multilayer Ceramic Chip Capacitors

A.【About the J-STD-020 Reflow profile 】

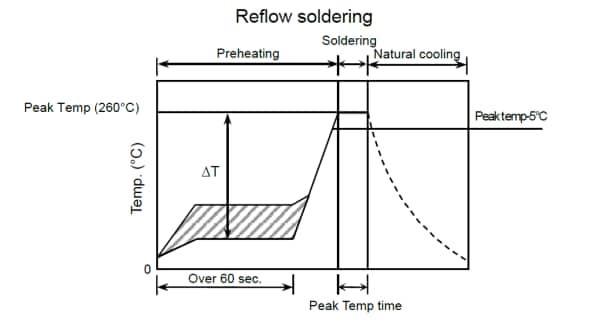

TDK MLCCs are compatible with the reflow condition defined in J-STD-020 by JEDEC (JEDEC Solid State Technology Association) below.

Depending upon the mounting conditions, such as solder type, solder amount and board design, mechanical/thermal stress levels should be considered.

Please verify the mounting conditions and performance by the actual circuit board.

【Profile Feature】

| Peak temp | Package thickness <2.5mm : 260℃ Package thickness >2.5mm : 250℃ (According to JEDEC J-STD-020, peak temperature 250℃ is applied for product > 2.5mm. In case of TDK MLCC, 260℃ is applicable also for >2.5mm also, except CKG Series.) |

|---|---|

| Time within peak temp-5℃ | 30sec Max. Package thickness 2.5mm and thinner : 255℃ Package thickness thicker than 2.5mm : 245℃ |

| Liquidus temp of solder | 217℃ (Sn-3.0Ag-0.5Cu) |

| Time above 217℃ | 60~150sec |

| Heating Gradient | - *1 |

| Cooling Gradient | Natural cooling *2 |

| Preheating condition | CGA5 (C3216) and smaller : ΔT≦150℃ CGA6 (C3225) and larger : ΔT≦130℃ |

- *1 : For heating gradient, please apply pre-heating with consideration of the gap of temperature DT between peak and pre-heat to avoid thermal shock.

- *2 : Natural cooling is recommended. In case of forced-air cooling, please confirm the mounting conditions and performance with consideration for solder type, solder amount, and board design.