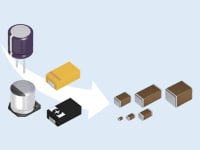

積層セラミックチップコンデンサ

CLLC1AX7S0G474M050AC

|

|

寸法

| 長さ(L) |

|

| 幅(W) |

|

| 厚み(T) |

|

| 端子幅(C) |

|

| 端子間隔(P) |

|

| 推奨ランドパターン(PA) |

|

| 推奨ランドパターン(PB) |

|

| 推奨ランドパターン(PC) |

|

| 推奨ランドパターン(PP) |

|

電気的特性

| 静電容量 |

|

| 定格電圧 |

|

| 温度特性 |

|

| 誘電正接 (Max.) |

|

| 絶縁抵抗 (Min.) |

|

その他

| 使用温度範囲 |

|

| はんだ付け方法 |

|

| AEC-Q200 |

|

| 包装形態 |

|

| 梱包数 |

|

製品情報

ドキュメント

技術支援ツール

おすすめコンテンツ

特性グラフ

グラフをローディング中...

この製品を見た人はこれらの製品も見ています

積層セラミックチップコンデンサ

C0510X5R1A474M030BC

Capacitance=470nF

Edc=10V

T.C.=X5R

LxWxT:0.52x1x0.3mm

Low ESL reverse geometry

積層セラミックチップコンデンサ

C0510X5R1C104M030BC

Capacitance=100nF

Edc=16V

T.C.=X5R

LxWxT:0.52x1x0.3mm

Low ESL reverse geometry

積層セラミックチップコンデンサ

C0510X6S0G104M030BC

Capacitance=100nF

Edc=4V

T.C.=X6S

LxWxT:0.52x1x0.3mm

Low ESL reverse geometry

積層セラミックチップコンデンサ

C0510X7R1E473M030BA

Capacitance=47nF

Edc=25V

T.C.=X7R

LxWxT:0.52x1x0.3mm

Low ESL reverse geometry

積層セラミックチップコンデンサ

CGAEB1X7T0G105M050BC

Capacitance=1μF

Edc=4V

T.C.=X7T

LxWxT:0.58x1.1x0.58mm

Low ESL reverse geometry

AEC-Q200

積層セラミックチップコンデンサ

CLLC1AX6S0G475M050AC

Capacitance=4.7μF

Edc=4V

T.C.=X6S

LxWxT:1.6x0.8x0.5mm

Ultra Low Inductance

積層セラミックチップコンデンサ

CLLC1AX7R0G104M050AC

Capacitance=0.1μF

Edc=4V

T.C.=X7R

LxWxT:1.6x0.8x0.5mm

Ultra Low Inductance

積層セラミックチップコンデンサ

CLLC1AX7S0G105M050AC

Capacitance=1μF

Edc=4V

T.C.=X7S

LxWxT:1.6x0.8x0.5mm

Ultra Low Inductance

積層セラミックチップコンデンサ

CLLC1AX7S0G225M050AC

Capacitance=2.2μF

Edc=4V

T.C.=X7S

LxWxT:1.6x0.8x0.5mm

Ultra Low Inductance

積層セラミックチップコンデンサ

CLLC1AX7S0G334M050AC

Capacitance=0.33μF

Edc=4V

T.C.=X7S

LxWxT:1.6x0.8x0.5mm

Ultra Low Inductance