静電気対策における積層チップバリスタと積層チップコンデンサの比較

積層チップコンデンサによる静電気対策

機器の静電気対策として、保護部品が用いられます。保護部品は、ICや電子部品を保護するために回路上へ設置され、スイッチやヘッドフォンジャックなどから侵入する静電気からICや周辺電子部品を保護します。保護部品は大きく4つに分類され、ツェナーダイオード(TVSダイオード)、積層チップバリスタ、ESDサプレッサ、積層チップコンデンサが挙げられます。挿入される静電容量に制限がない場合、積層チップコンデンサが使用されることが多くあります。

積層チップコンデンサは静電容量が大きいほど静電気吸収能力が高いため、より大きな静電容量の部品が選定されます。しかし、エンドユーザーの設計変更で、より通信速度が速いICへの切り替えなどが行われると、大きな静電容量の影響により信号がなまってしまう場合があります(図1)。これを改善するために静電容量が小さい積層チップコンデンサへ切り替えた場合、静電気対策が十分でなくなってしまう可能性があります。この場合、積層チップコンデンサ以外の保護部品を選定しなければいけません。

本資料では、各種保護部品の特徴及び、積層チップコンデンサと積層チップバリスタの静電気吸収能力の違いを説明します。

図1 速度の違いによる信号のなまり

関連リンク

プロダクトオーバービュー

ESD対策に使用される各種保護部品の特徴

ESD などのサージから半導体デバイスや回路を守るために、積層チップコンデンサ、ESDサプレッサ、TVSダイオード、積層チップバリスタなどの保護部品が用いられます。それらの特徴を以下にまとめました (表1)。

| タイプ | L x W寸法 | 静電容量(pF) | 特徴 | |||

|---|---|---|---|---|---|---|

| 1以下 | 1~50 | 50~100 | 100以上 | |||

| 積層チップバリスタ | 0.4mm x 0.2mm [EIA01005] 以上 |

○ | ○ | ○ |

|

|

| TVSダイオード | 0.6mm x 0.3mm [EIA0201] 以上 |

○ | ○ | ○ |

|

|

| ESDサプレッサ | 0.6mm x 0.3mm [EIA0201] 以上 |

○ |

|

|||

| 積層チップコンデンサ(静電気対策用) | 1.6mm x 0.8mm [EIA0603] 以上 |

○ |

|

|||

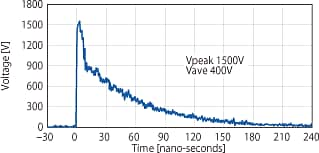

図2は、各種保護部品を用いた場合のESD吸収波形を示します。IEC61000-4-2に基づきHBM(Human Body Model:人体モデル)を用いてESD波形を発生させ、保護部品による静電気吸収能力を評価しています。横軸は時間(ns), 縦軸は電圧(V)を表しています。この電圧が、静電気が発生した場合にICに印加される電圧と考えられ、電圧値が小さくなるほど静電気からの保護能力が高いと言えます。

- 保護部品なしの場合(ESDシミュレータ充電電圧8kV, 150pF, 330Ω, 接触放電)、急峻な初期ピーク電圧の立ち上がり後、徐々に電圧値が降下していくパルスサージ波形で、ピーク電圧(Vpeak)は1,500Vにも及び、30nsから100nsの平均電圧(Vave)も400Vのレベルとなります。

- ESDサプレッサは印加電圧を上げていったとき、ある電圧で短絡して急激に電流が流れ出すタイプの保護素子で、その電圧をトリガー電圧といいます。ESDサプレッサは、Vaveを29Vまで抑制できますが、トリガー電圧の関係上、Vpeakは約500V程度までしか抑制できません。

- 積層チップコンデンサは、静電容量成分がESDの放電電荷をチャージすることで電圧を抑制します。そのため、静電容量が大きいほどESD抑制能力が高くなります。Vpeakを約23V まで抑制できますが、その後はチャージした電荷を放出するために数百ナノ秒後に大きな電圧ピークが発生します。

- TVSダイオードは、ツェナーダイオード(定電圧ダイオード)から派生したESD対策用の保護部品で、過渡電圧サプレッサとも呼ばれています。そのESD吸収波形はVpeak、Vaveともに低く、すぐれた特性を示します。

- 積層チップバリスタもTVSダイオード同様、Vpeak, Vaveともに低い特性を示しています。加えて積層チップバリスタは静電容量成分を持っているため、Vpeakの抑制においてTVSダイオードより有利となります。ただし、積層チップバリスタは静電容量が大きいほどESD抑制効果も大きくなる傾向があるので、あまり大きい静電容量が入れられない高速信号回路においてはTVSダイオードのほうが優れた特性を示します。

また、図3にアプリケーションごとの最適な保護部品マップを示します。横軸は信号速度、縦軸は静電気吸収性能を示しています。また、下段には規格ごとの通信速度を示します。このグラフでは、規格毎に最適な保護部品を選定することができます。1Mbps以下の信号ラインでは、積層チップコンデンサを使用することができます。より高速の信号ラインで使用したい場合は、チップバリスタ、TVSダイオード、ESDサプレッサなどが適しています。図3にあるように、TDKのチップバリスタにはAVRMシリーズとAVRLシリーズがあります。AVRMシリーズは、高静電容量・高静電気吸収能力を特徴としており、約10kbps~100Mbpsの信号ラインにおいて、高い静電気吸収を実現しています。一方、AVRLシリーズは、低静電容量を特徴としており、更に高い周波数約50Mbps~約1GbpsにおいてESDサプレッサより高い静電気吸収能力を示します。

チッププロテクタは、低静電容量・高静電気吸収能力を特徴としておりTVSダイオードの置換に適しております。約10Mbps~1Gbpsにおいて、ESDサプレッサはもとよりAVRLシリーズより更に高い静電気吸収能力を示します。

図3 アプリケーション毎の最適な保護部品マップ

チップバリスタは、AVRM/AVR-Mシリーズ、AVRLシリーズ、AVRHシリーズがあります。

AVRM/AVR-Mシリーズは、高静電容量・高静電気吸収能力を特徴とします。10kbps~10Mbpsの通信ラインにおいて、高い静電気吸収を実現出来ます。

AVRLシリーズは、低静電容量を特徴としております。この事により、更に速い50Mbps~1Gbpsの通信ラインにおいてESDサプレッサーより高い静電気吸収能力を示します。

AVRHシリーズは、EIA0402(1005mm)サイズ以下のAEC-Q200に準拠した車載用チップバリスタになります。

チッププロテクタは、低静電容量・高静電気吸収能力を特徴としておりTVSダイオードの置換に適しております。

50Mbps~500Mbpsの通信ラインにおいて、ESDサプレッサーはもとよりAVRLシリーズより更に高い静電気吸収能力を示します。

また高静電気吸収能力に特化した チップコンデンサCGA3EA シリーズにより1Mbps以下の比較的低い通信ラインでの静電気保護対策に適しています。

関連リンク

アプリケーションノート

静電容量の違いによるESD吸収波形の違い

積層チップコンデンサは、その静電容量の大きさで静電気吸収能力が大きく変わってきます。静電容量が高くなるにつれ、静電気吸収能力は向上します。図4にチップコンデンサの静電容量別のESD吸収波形を示します。

IEC61000-4-2に基づきHBM(Human Body Model:人体モデル)を用いて4kVのESD波形を発生させ、保護部品による静電気吸収能力を評価しました。横軸は時間(ns), 縦軸は電圧(V)を表しています。100pFの積層チップコンデンサでは、Peak電圧が662Vとなります。1000pFでは350V, 10nFでは155V、100nFでは10Vとなっています。100nFでは非常に高い静電気吸収能力を示していますが、電源ライン以外の通信ラインでは信号をなまらせてしまい使用できなくなる場合が多くあります。一方、100pFまで静電容量を下げると、通信速度の観点からAudioやVideoラインでの使用は可能ですが、静電気吸収能力はほとんどなくなってしまいます。このことから、電源ライン以外で静電気対策を行う場合、積層チップコンデンサ以外の保護部品を選定する必要があります。

関連リンク

セレクションガイド

同静電容量を持つ積層チップコンデンサと積層チップバリスタの静電気吸収能力

図5に同じ静電容量を持つ積層チップコンデンサと積層チップバリスタのESD吸収波形を示します。こちらのグラフも、上記のグラフと同様にIEC61000-4-2に基づきHBM(Human Body Model:人体モデル)を用いて4kVのESD波形を発生させ、保護部品による静電気吸収能力を評価しています。

積層チップコンデンサはピーク電圧が662Vであるのに対して、積層チップバリスタは37Vと非常に小さい値となっています。前述のように積層チップコンデンサは静電気が印加された場合素子内部に電気をため込みます。そのため、高い静電気吸収能力を得るためには、高い静電容量を必要とします。一方、積層チップバリスタは過電圧がかかった場合、素子自体の抵抗が下がる特性を持っているため高い静電容量を必要としません。同静電容量の場合、積層チップバリスタは積層チップコンデンサと比較し非常に高い静電気保護能力を持つため、静電容量による制限がありチップコンデンサが使用できなくなった場合はチップバリスタを選定すると良いと思われます。

関連リンク

セレクションガイド

積層チップバリスタの選定ポイント

静電気対策用に積層チップバリスタを選定する際のキーポイントについて概説します。もっとも重視する点は、機器のESD耐量をアップさせることです。できるだけバリスタ電圧が低い製品を選定することで、すぐれた静電気吸収能力が得られますが、保護すべき回路の電圧値に合わせて最適な値を選択する必要があります。また、同じバリスタ電圧であれば、静電容量が大きいほど、静電気吸収能力や静電気耐久性が向上します。ただし、チップコンデンサと同様に静電容量が大きいほど信号品質が劣化してしまうので、信号に影響を与えない範囲で、できるだけ静電容量の大きい製品の選定を行います。表2にTDKチップバリスタの製品ラインナップを示します。

| シリーズ | LxW寸法 | 最大許容回路電圧 [DC](V) |

バリスタ電圧 [@1mA](V) |

静電容量 (pF) |

対応通信速度 |

|---|---|---|---|---|---|

| AVRMシリーズ | 0.4x0.2~2.0x1.2mm [EIA01005~EIA0805] |

3.5~28 | 6.8~39 | 15~1050 | 10kbps~100Mbps |

| AVRLシリーズ | 0.4x0.2~1.6x0.8mm [EIA01005~EIA0805] |

10~25 | 27~90 | 0.5~6.8 | 50Mbps~1Gbps |

| SGNEシリーズ | 0.4x0.2~0.6x0.3mm [EIA01005~EIA0201] |

4.3~15 | 8~27 | 6.8~15 | 50Mbps~500Mbps |

![図4 積層チップコンデンサの静電容量別ESD吸収波形 [部品なし]](/system/files/apn_comp_chip-varistor_mlcc_tec00009_ja.png)

![図4 積層チップコンデンサの静電容量別ESD吸収波形 [MLCC 100pF]](/system/files/apn_comp_chip-varistor_mlcc_tec00010_ja.png)

![図4 積層チップコンデンサの静電容量別ESD吸収波形 [MLCC 1000pF]](/system/files/apn_comp_chip-varistor_mlcc_tec00011_ja.png)

![図4 積層チップコンデンサの静電容量別ESD吸収波形 [MLCC 10nF]](/system/files/apn_comp_chip-varistor_mlcc_tec00012_ja.png)

![図4 積層チップコンデンサの静電容量別ESD吸収波形 [MLCC 100nF]](/system/files/apn_comp_chip-varistor_mlcc_tec00013_ja.png)

![図4 積層チップコンデンサの静電容量別ESD吸収波形 [Based on IEC61000-4-2 150pF, 330ohm, Contact, ESD Voltage = 4kV]](/system/files/apn_comp_chip-varistor_mlcc_tec00014_ja.png)

![図5 同静電容量を持つ積層チップコンデンサと積層チップバリスタのESD吸収波形 [MLCC 100pF]](/system/files/apn_comp_chip-varistor_mlcc_tec00016_ja.png)

![図5 同静電容量を持つ積層チップコンデンサと積層チップバリスタのESD吸収波形 [AVRM0603C6R8NT101N]](/system/files/apn_comp_chip-varistor_mlcc_tec00015_ja.png)