ESD保護素子の配置/レイアウトの重要性|静電気の見える化

しかし、ESDの侵入経路の特定は難しく、実装したESD保護素子が本来の実力を発揮していないケースが多くみられます。

その為、本来の実力を発揮させるためには、ESD侵入経路を特定して、ESD発生源の近くに実装する必要があります。

そこで今回、実装配置の重要性の調査を、ESD可視化装置を用いて行いましたので、ご紹介します。

目次

紹介動画 (2:35)

ESD可視化装置-基板レイアウトの最適化-

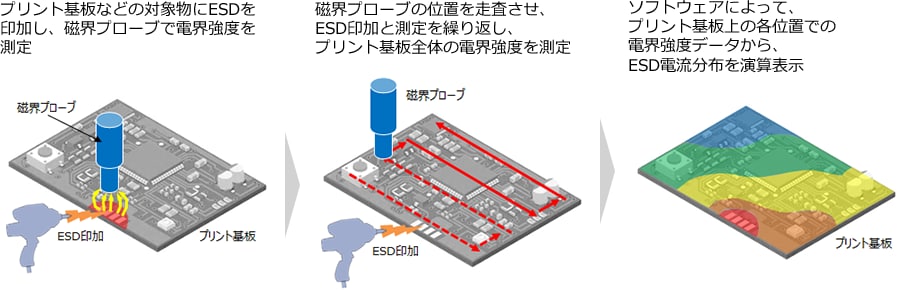

ESD可視化装置とは、ESDの流れを非接触の磁界プローブで自動走査させ、ESD電流の可視化を行うことができる装置です。

走査領域内での電界強度分布を取得することができる為、ESD対策における基板レイアウトの最適化に有効なツールとなります。

この装置を用いて、ESD保護素子の実装配置の違いにおける、基板上でのESD挙動を観測しました。

実装配置の違いによるESD挙動 (積層チップバリスタ)

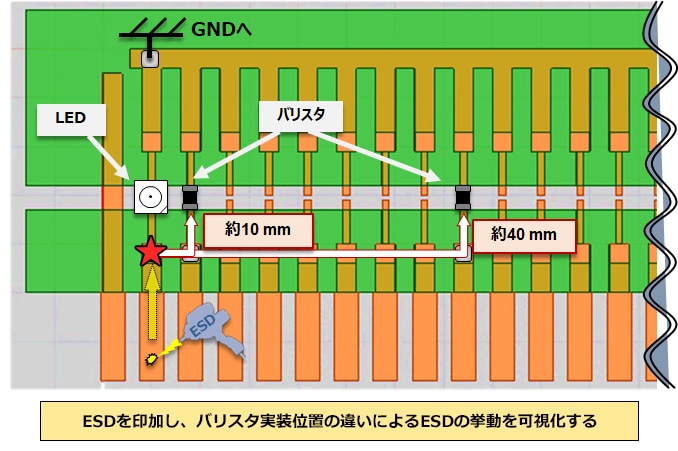

下記のような基板を用いてESDの挙動の評価を行いました。

保護対象製品はLEDを使用し、ESD保護素子は積層チップバリスタを使用しました。

下図の支点(★)から約10mmと約40mmの位置にチップバリスタを実装し、それぞれのESD挙動を観測しました。

検証条件

- ◆ ESD印加電圧:+1kV

- ◆ 基板:FR-4 / Cu ランドパターン

- ◆ ランドパターン:複数の実装ラインが並列に連なるパターン

- ◆ ESD対策部品:チップバリスタ (1608形状 / 27V / 430pF)

- ◆ 保護対象:LED (ESD耐量6kV)

- ◆ 実装位置:並列の支点 (図の★) から約10mm, 40mm

積層チップバリスタを約10mm (左) と約40mm (右) の位置に実装した際のESD挙動です。

近くに置いた方が、ESDがチップバリスタの方に流れ、LEDラインに流れていないことが分かります。

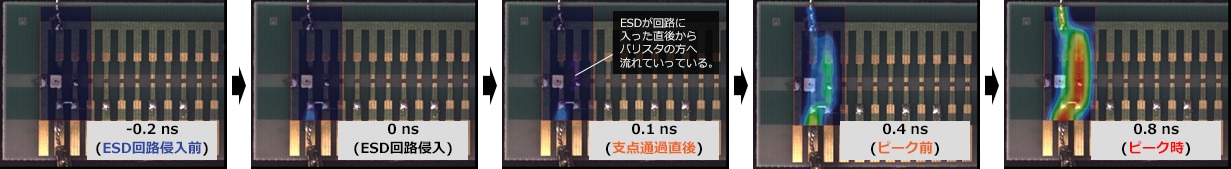

[ 実装位置:10mm ]

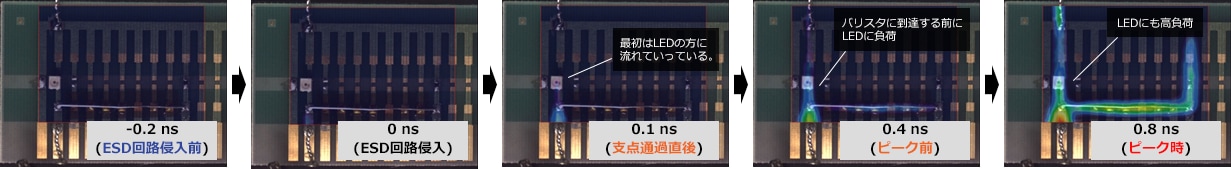

[ 実装位置:40mm ]

チップバリスタの実装位置が支点から約10mmの場合では、ESDは回路に侵入した直後からチップバリスタ実装ラインに流れ、

ピーク時点においても、チップバリスタ実装ラインへ支配的に流れている様子が分かります。

<ESD印加前後のタイムラプス (実装位置 : 10 mm) >

一方、チップバリスタの実装位置が支点から約40mmの場合では、ESDは回路に侵入した直後にLEDのラインへ流れ、ピーク時点でもLEDのラインへ流れている様子が分かります。

つまり、比較的高い電気的負荷がLEDに掛かっていることを示唆しています。

<ESD印加前後のタイムラプス (実装位置 : 40mm) >

ESD対策におけるチップバリスタの最適な実装配置

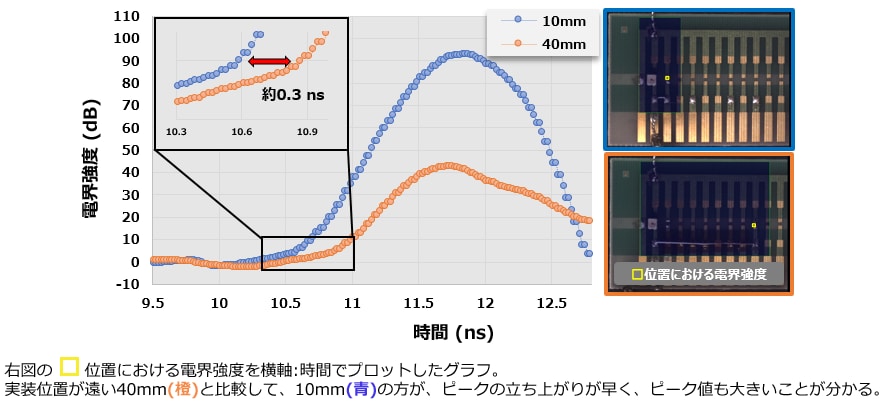

チップバリスタ実装箇所のおける電界強度を解析したところ、10mm (青色) の方が約0.3nsも早くESDを誘導していました。

ピーク到達が約1nsのESDにおいては、この0.3nsという時間は非常に大きな差となります。

加えて、ESDを早く誘導できている為、ピーク時の電界強度も大きくなっていることが分かります。

つまり、ESD侵入源近くにチップバリスタを実装した方が、チップバリスタへより多くのESDを誘導することができるということです。

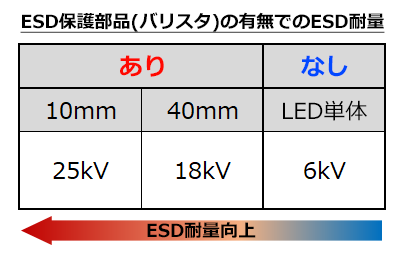

上記の検証条件下で、実際にESD耐量を測定したところ、ESD保護部品が実装され、実装配置がESD侵入源に近い方が、ESD耐量が向上することが分かりました。

したがって、より良いESD対策の為には、チップバリスタの実装配置をESD侵入源の近くにすることが最適であるということです。

ESD印加条件

- ◆ ESD規格:IEC61000-4-2 HBM (150pF/330Ω)

- ◆ 極性・回数:両極性(±)を10回ずつ

最適なESD対策と基板レイアウトを可能にするTDK製チップバリスタ

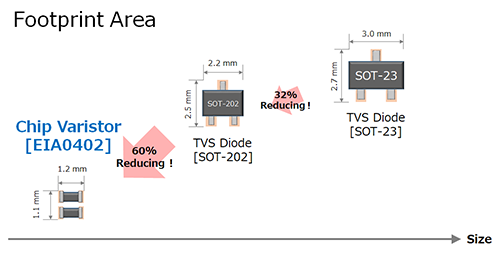

基板の複雑化に伴い、ESD侵入源の特定ができても、近くの実装スペースに制約が生じる場合があります。

TDKの積層チップバリスタは小型サイズまでラインナップがあることが特徴の一つです。

TDKでは現在、民生向けでは最小サイズEIA01005 (0.4 x 0.2 mm) まで、車載向けでは、業界最小サイズとなるEIA0402 (1.0 x 0.5mm) までのチップバリスタを量産化しています。

したがって、TDKチップバリスタを用いれば、省スペース化を図ることができ、自由度の高い実装配置が可能となります。