ノイズ対策とMLCC員数削減に適した3端子貫通型フィルタ "YFFシリーズ"とは?

また、自動車の電装システムにおいても、安全・快適性の向上やインフォテインメント化に対応するため、低ESLタイプのニーズが高まっています。

本ソリューションガイドではTDKの先進の低ESL部品である3端子貫通型フィルタ“YFFシリーズ”を使用した各種ソリューションをご紹介します。

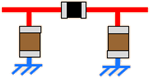

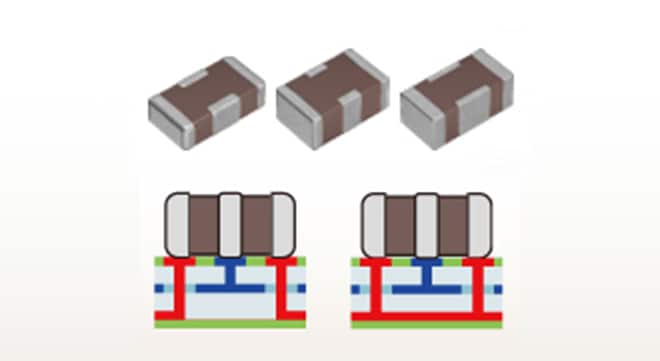

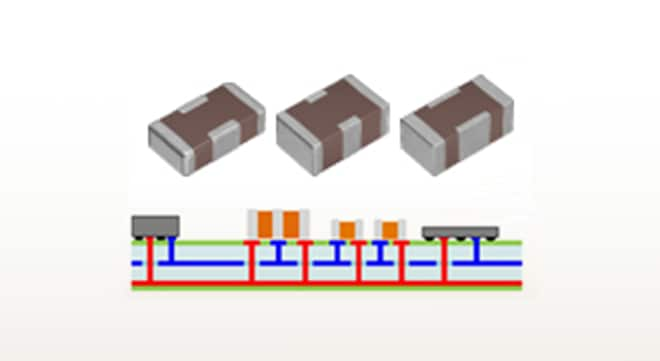

3端子貫通型フィルタの構造

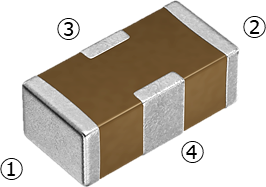

3端子貫通型フィルタの外観、内部構造の概念図を示します。

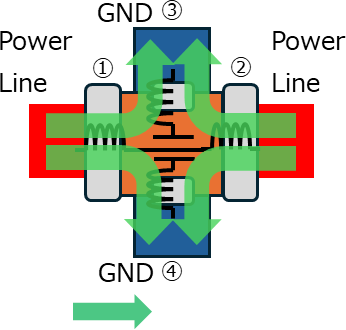

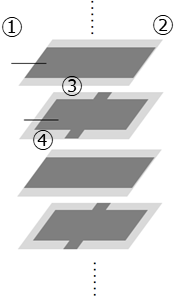

一般に3端子と呼ばれますが、実際は2つの端子電極と2つのグラウンド電極からなり、内部は通電用内部電極とグラウンド用内部電極を交互に積層した構造となっています。

外観

端子電極 端子電極 グラウンド電極 グラウンド電極ノイズ電流経路イメージ

:ノイズ電流内部構造(模式図)

通電用内部電極 グラウンド用

内部電極

貫通型構造により、コンデンサとグラウンドの距離が短くなり低ESL化し、ノイズ抑制効果が高まります。

グラウンド電極が2か所あることで、並列効果により、さらに低ESL化します。

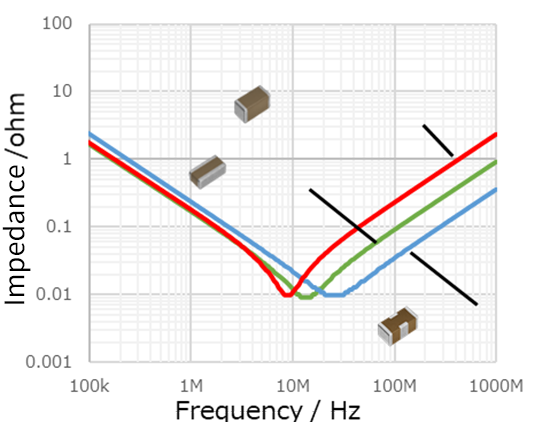

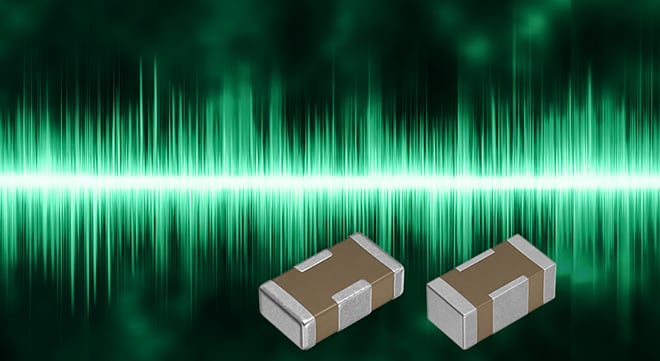

インピーダンス-周波数特性の他MLCCとの比較例

高周波ノイズ除去用のコンデンサとしての特性は、ESR(等価直列抵抗)やESLが低く、自己共振周波数がより高いものが求められます。

ESRやESLは端子電極や内部電極の抵抗成分やインダクタンス成分によるものです。

そこで、通常の2端子MLCC(積層セラミックチップコンデンサ)の端子電極の長手方向と幅方向を逆転(フリップ)し、電流方向を太く短くすることで低ESL化を図ったフリップコンデンサもノイズ対策用として有効な手段です。

こうしたフリップコンデンサよりも、さらに低ESR・低ESLを実現したのが、TDKの3端子貫通型フィルタYFFシリーズです。

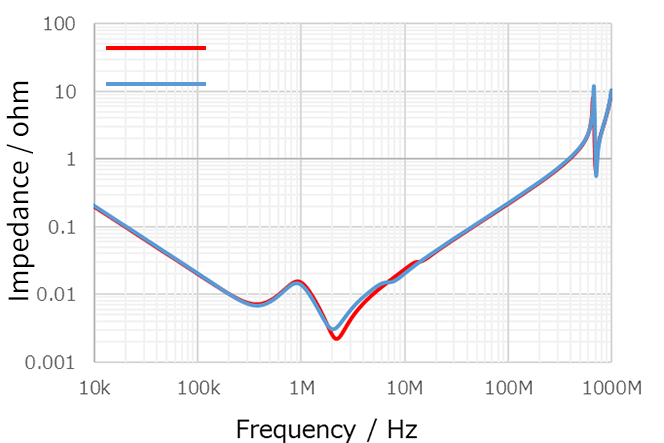

TDKの2端子MLCC、フリップコンデンサ、そして3端子貫通型フィルタのインピーダンス-周波数特性およびESL値の単品の比較例を図2に示します。

3端子貫通型フィルタのESL値は通常2端子MLCC、フリップコンデンサと比較して低いです。

3端子貫通型フィルタの用途及び期待される効果

デカップリング、フィルタ、DC/DCコンバータの各用途におけるソリューション事例をご紹介します。

デカップリング用途におけるソリューション事例

電源ラインの電圧変動は、回路の動作を不安定にしたり、ノイズの原因となります。そこで、電源ラインとグラウンドの間にコンデンサを挿入し、負荷が急激に変化したときに、電流を一時的に供給して電圧変動を抑制します。これをデカップリングといい、使用されるコンデンサをデカップリングコンデンサといいます。

近年、SoCの高電力化、高周波化、微細化に伴う低電圧化に伴い、ターゲットインピーダンスをクリアするためのデカップリングコンデンサの員数も増加傾向にあります。低ESLを特徴とする3端子貫通型フィルタ YFFシリーズは従来の2端子コンデンサからの置換によって員数減に効果を発揮します。

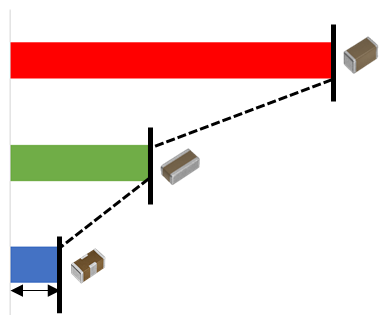

通常、幅広い周波数帯域を低インピーダンス化するために容量の異なるMLCCを複数個並列させます。

以下の通り、低ESLを特徴とする3端子貫通型フィルタを使用することで、員数減の効果を得る事がわかります。

インピーダンス比較

1uF/100nF/10nF/1nF (4pcs) 3端子貫通型フィルタ/1005mm(0402inch)/

1uF (1pc)

搭載員数減の効果を得る事ができます

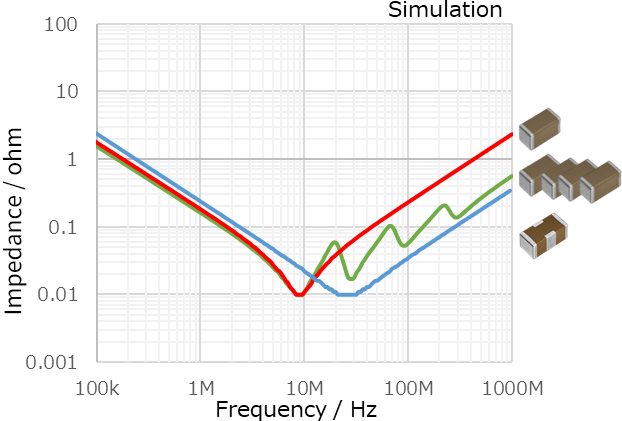

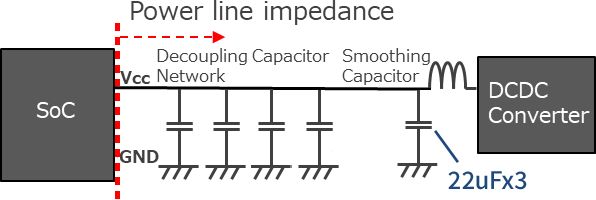

デカップリング用途における3端子貫通型フィルタによる員数減の事例をPIシミュレーションを用いて示します。

ここではSoC側から見たインピーダンスデータを比較します。

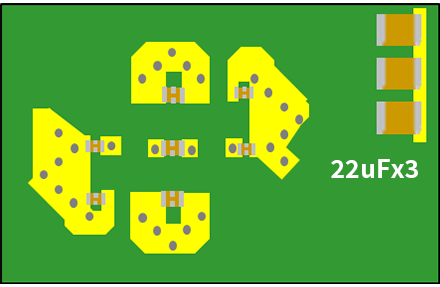

提案前後の構成の共通事項として、DC/DCコンバータには22uFのMLCC3個がDC/DCコンバータの平滑用として接続されている事を想定します。

回路イメージ

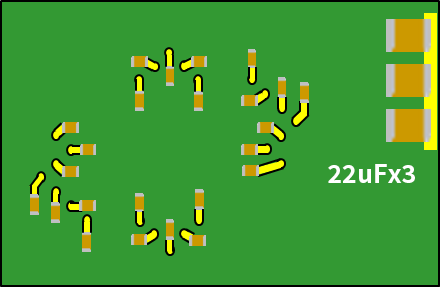

現行構成とTDK提案構成

現行構成

2端子1005mm(0402inch) x24pcs

TDK提案構成

3端子1608mm(0603inch) x3pcs

3端子1005mm(0402inch) x4pcs

現行構成とTDK提案構成はほぼ同特性であることが判ります。

現行構成

| 端子構造 | 品種 (mm/inch) |

容量 (uF) |

数量 (pcs) |

合計容量 (uF) |

実装面積 (mm2) |

|---|---|---|---|---|---|

| 2端子 | 1005/0402 | 1 | 16 | 16 | 8 |

| 2端子 | 1005/0402 | 0.1 | 8 | 0.8 | 4 |

| 現行構成 | 24 | 16.8 | 12 | ||

員数 -17pcs,実装面積-51%

TDK提案構成

| 端子構造 | 品種 (mm/inch) |

容量 (uF) |

数量 (pcs) |

合計容量 (uF) |

実装面積 (mm2) |

|---|---|---|---|---|---|

| 3端子 | 1608/0603 | 4.7 | 3 | 14.1 | 3.84 |

| 3端子 | 1005/0402 | 1 | 4 | 4 | 2 |

| TDK提案構成 | 7 | 18.1 | 5.84 | ||

2端子MLCCから3端子貫通型フィルタに置換する事により実装数の員数減への効果が期待できます。ただし実回路上では、基板パターンの電気的成分が加わりますので、基板レイアウトによって、デカップリングコンデンサの最適員数構成は変わります。

TDKではPIシミュレーションを通じた3端子貫通フィルタへの置換シミュレーションサービスを無償で提供しております。詳細は弊社までお問合せください。

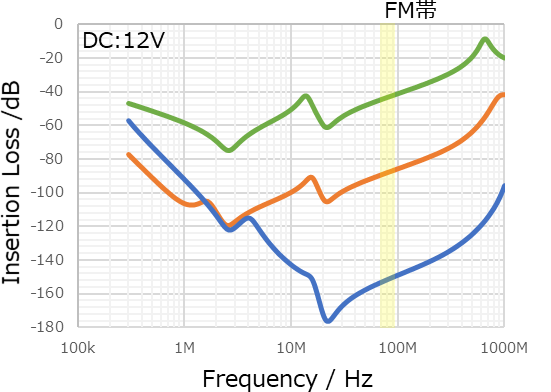

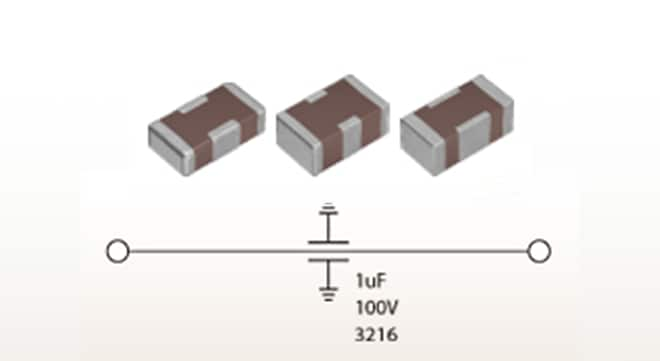

フィルタ用途におけるソリューション事例

近年電源ICの高周波化に伴い、高周波ノイズが問題になっており、セットの異常動作を引き起こす原因となります。

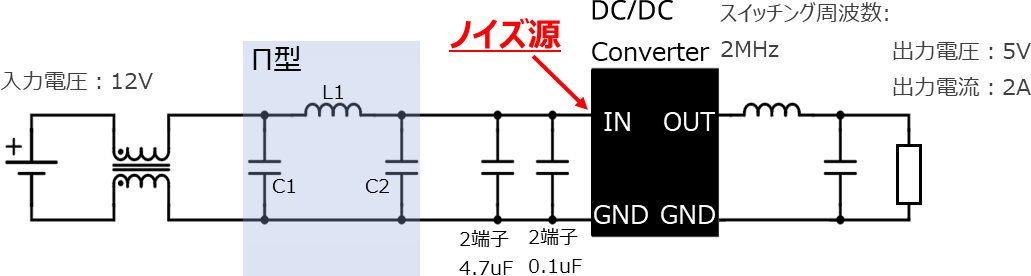

ノイズ対策として一般的には、C-L-Cのπ型フィルタを電源ライン上に構成することにより対策を施しますが、フィルタのコンデンサに3端子貫通型フィルタを組み込むことで高い減衰効果を得る事が可能となります。

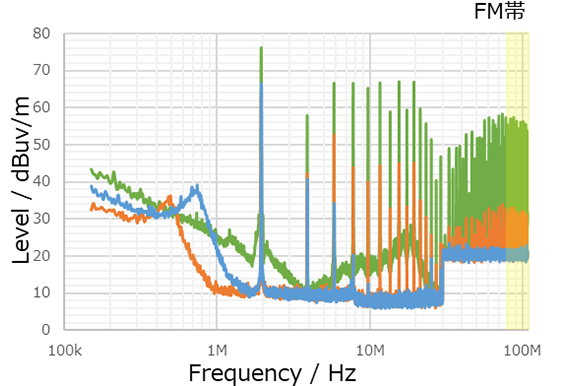

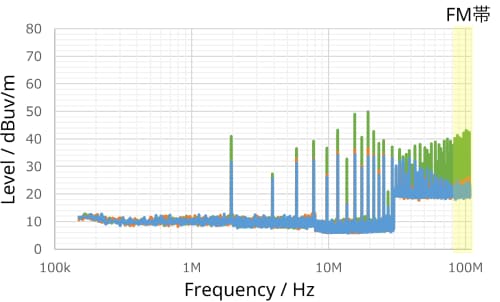

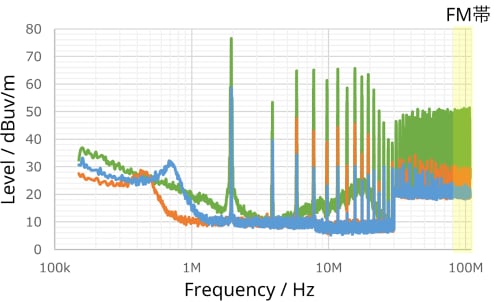

図8にSimulationによる伝達特性の結果、図9にDC/DCコンバータの実機を使用し、各ノイズモードで発生する伝導ノイズ(電圧法)を測定しました。

なお、図9伝導ノイズ電圧法に関しては3構成共にコモンモード対策として弊社コモンモードフィルタを搭載した状態で測定しています。

測定条件および回路図

| Π型フィルタ構成 | 1 | 2 | 3 |

|---|---|---|---|

| 配線イメージ | ※フィルタなし | ||

| C1 | - | 2端子コンデンサ 3216mm(1206inch) , 4.7uF , 35V |

3端子貫通型フィルタ 3216mm(1206inch) , 1uF , 100V , 6A YFF31AH2A105M フィードスルー接続 * |

| L1 | - | フェライトビーズ 2.0×1.2mm, 220Ω at 100MHz, 3A |

フェライトビーズ 2.0×1.2mm, 220Ω at 100MHz, 3A |

| C2 | - | 2端子コンデンサ 3216mm(1206inch) , 4.7uF , 35V |

3端子貫通型フィルタ 3216mm(1206inch) , 1uF , 100V , 6A YFF31AH2A105M フィードスルー接続* |

*フィードスルー接続に関しては以下リンクを参照ください。

接続方法について

*フィルタ+2端子MLCC 4.7uF + 2端子MLCC 0.1uFを含んだ挿入損失になります。

挿入損失比較

82MHz 比較

構成1:-43dB

構成2:-87dB

構成3:-151dB

-44dB -64dB3端子を組み込むことで

高い減衰特性を得れます。

構成1:フィルタ無し

構成2:コンデンサ(2端子)

構成3:3端子貫通型フィルタ

ノーマルモード

本DC/DCコンバータの評価環境では

ノーマルモードノイズが大きい事が判ります。

82MHz 比較

構成1:54dBuV/m

構成2:30dBuV/m

構成3:20dBuV/m

-24dB -10dB特にノーマルモードノイズにおいて3端子を組み込むことで高いノイズ除去効果を得れます。

構成1:フィルタ無し

構成2:コンデンサ(2端子)

構成3:3端子貫通型

フィルタ

コモンモード

コモンモード+ノーマルモード

3端子貫通型フィルタをフィルタに組み込むことによって広範囲な周波数領域で高い減衰効果を得れます。

DC/DCコンバータ用途におけるソリューション事例

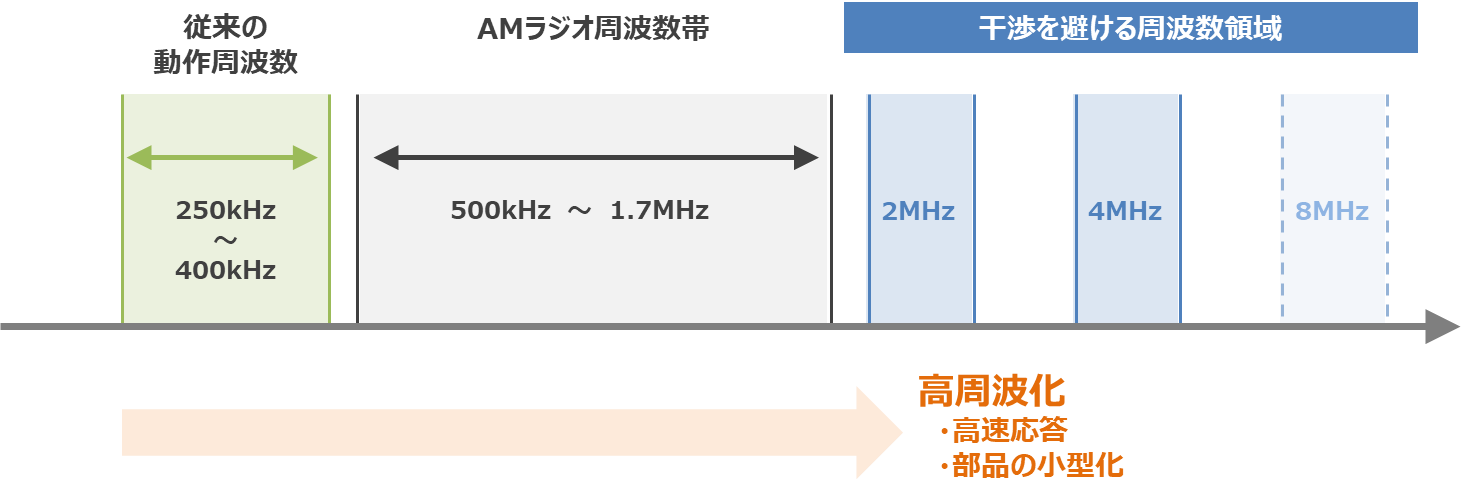

DC/DCコンバータのスイッチング周波数は、部品の小型化や高速応答が得られ、またAMラジオ周波数帯への干渉を避けるため、以下の通り従来の数百kHzから2MHz以上の周波数へと高周波化しています。

その結果、リップルノイズやリンギングノイズの周波数も高周波化することになり、数百MHz帯の高周波領域まで広帯域のノイズ対策が求められるようになりました。

本事例ではDC/DCコンバータの入力側、出力側に3端子貫通型フィルタを使用することによる電源変動の抑制や員数減に対しての効果を紹介します。

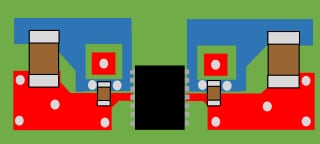

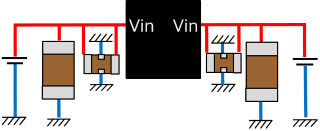

DC/DCコンバータ入力端子直近に3端子貫通型フィルタを配置した事例

DC/DCコンバータの入力端子は基本周波数からなるN次高調波は配線やICの寄生成分によるスイッチングノイズによって大きな高周波ノイズが発生し外部回路に放射される恐れがあります。通常このノイズはICの根元から断つ必要性があり、一般的にはIC直近に小型のセラミックコンデンサを入れて対策しますが、3端子貫通型フィルタを使用したDC/DCコンバータの事例を紹介します。なお、本DC/DCコンバータにはリファレンスとして3端子貫通型フィルタがIC直近のノイズ対策として使用されております。両構成の共通事項として入力コンデンサに2端子MLCC 10uFが端子両側に搭載されております。

| DC/DCコンバータ仕様 / 入力電圧:5V 出力電圧:0.8V SW周波数:2MHz 出力電流:4A | ||

|---|---|---|

| 構成 | 2端子MLCC 1005mm/0402inch, 100nF,50V x 1pc シャントスルー接続 |

3端子貫通型フィルタ YFF18AC1A104M 1608mm/0603inch , 100nF ,10V x 1pc シャントスルー接続 |

| 配線イメージ | 電源片側は内層にて接続 |

|

| 回路図イメージ | ||

*シャントスルー接続に関しては以下リンクを参照ください。

接続方法について

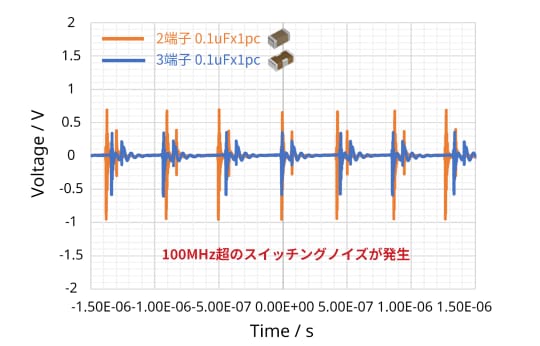

電圧波形比較

2端子

0.1uFx1pc

1.64Vpp

3端子

0.1uFx1pc

0.92Vpp

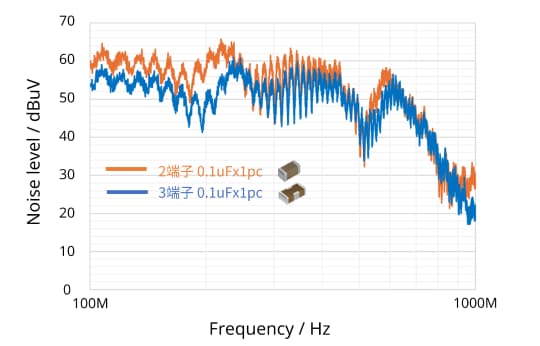

伝導ノイズ比較

2端子

0.1uFx1pc

65dBuVmax

3端子

0.1uFx1pc

60dBuVmax

3端子は電圧変動とノイズレベルの抑制が可能です。

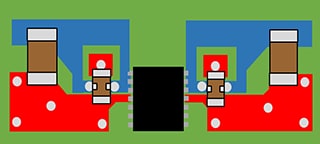

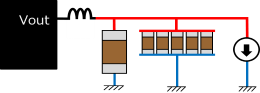

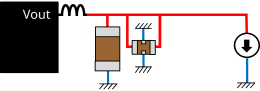

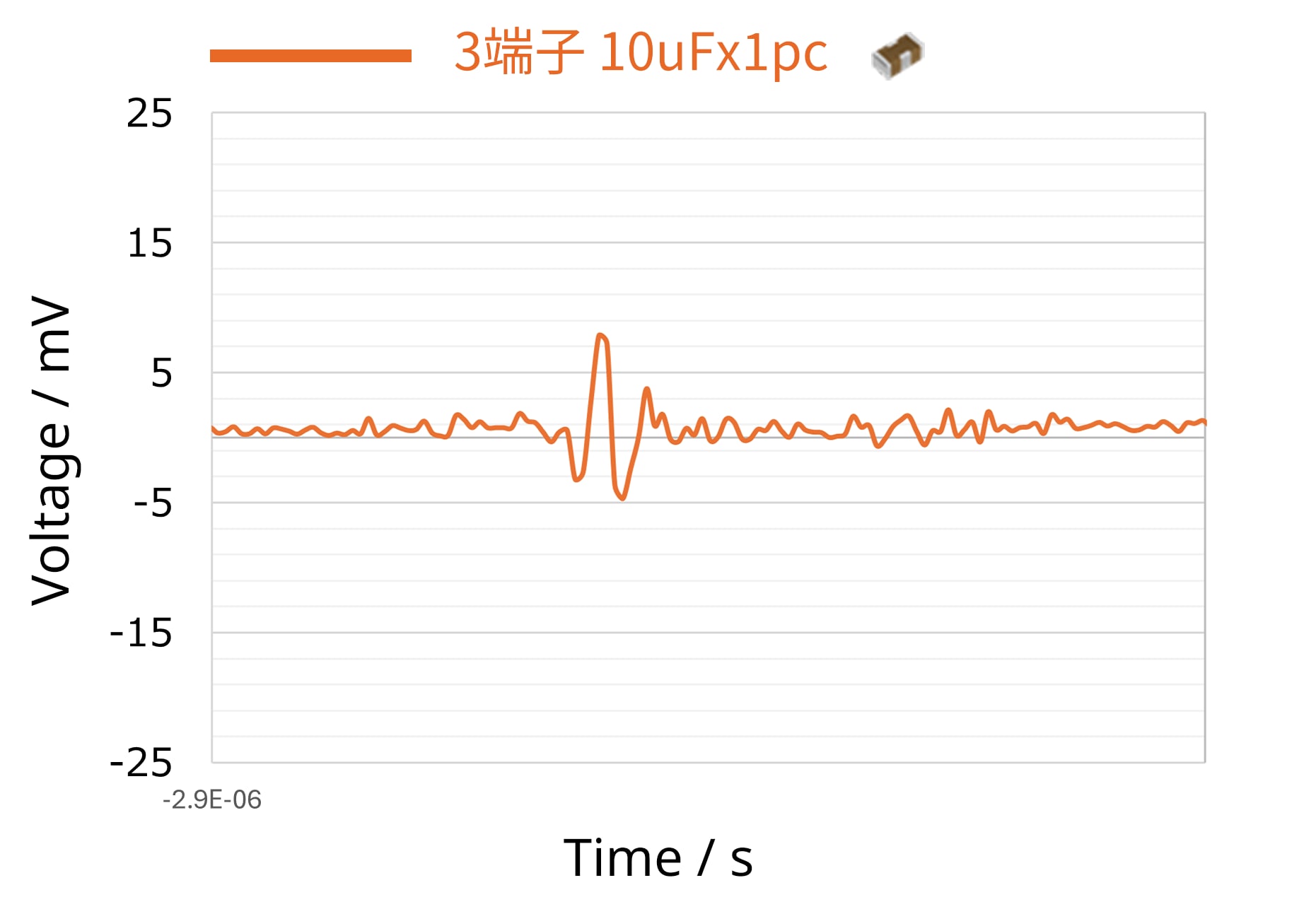

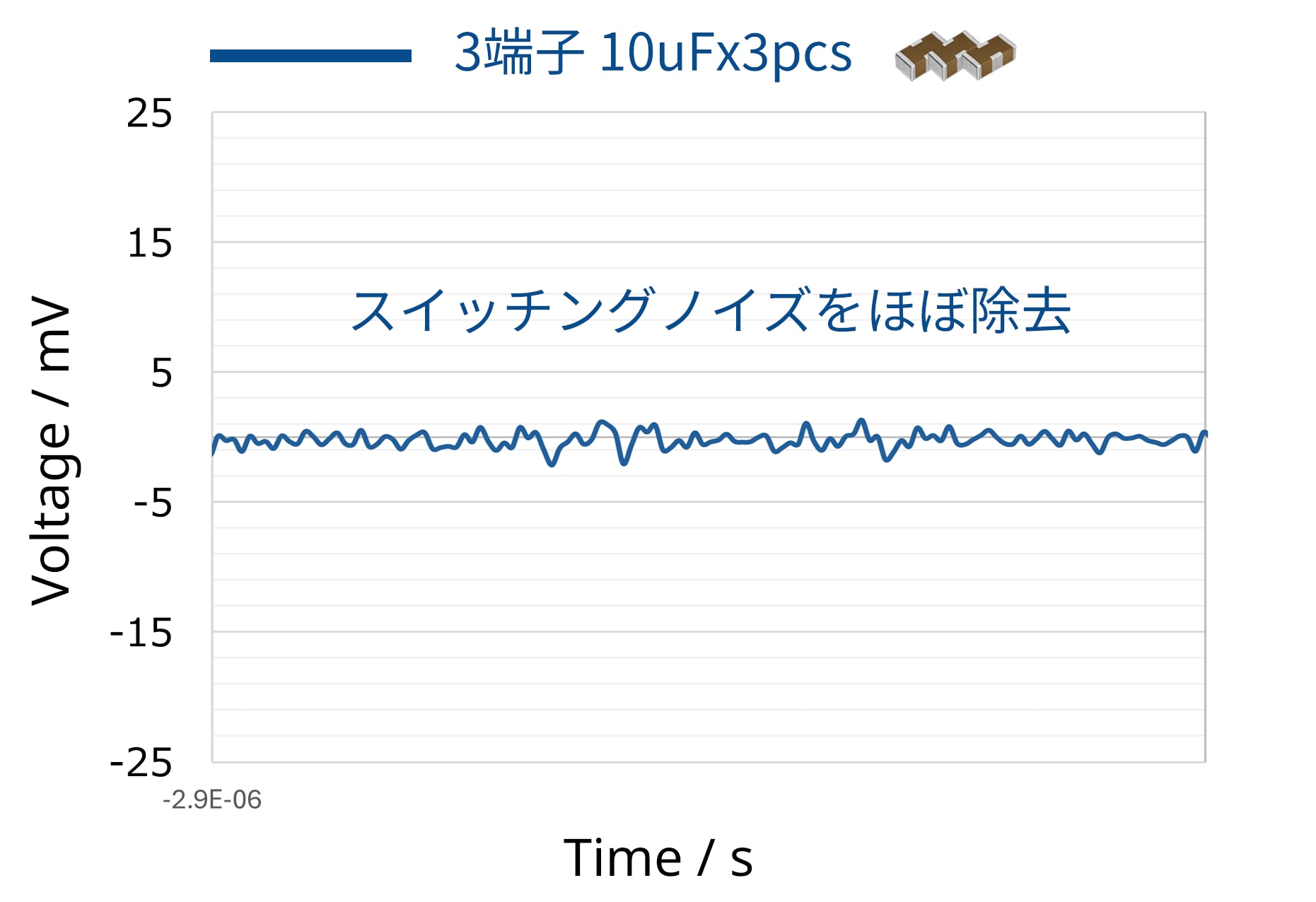

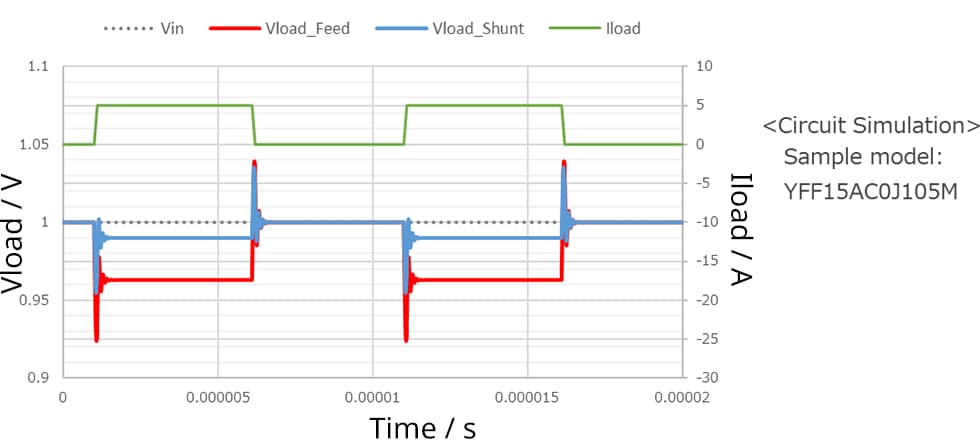

DC/DCコンバータ出力側に3端子貫通型フィルタを配置した事例

DC/DCコンバータの出力側についても基本周波数からなるN次高調波や配線やICの寄生成分によるスイッチングノイズによって大きな高周波ノイズが発生し外部回路に放射される恐れがあります。

SoCの低電圧化に伴い最大/最小電圧のマージンが減り、またセットの高機能化に伴い、高周波ノイズにセンシティブなセットが増えております。SoC側で対応する手法と併せ、ノイズの根本である電源IC側で対策をする事が望ましいと考えられます。ノイズ除去手法は従来2端子MLCCを多段に配置する事が有効でしたが、TDKの大容量3端子貫通型フィルタを使用することで、電源変動の抑制が可能となる事例をご紹介します。両構成の共通事項として出力コンデンサに2端子MLCC 47uFx1pc が搭載されております。

| 構成 | 2端子 MLCC 1608mm/0603inch, 1uF, 16V x 5pcs |

3端子貫通型フィルタ YFF18AC0G106M 1608mm/0603inch, 10uF, 4V x1 pc シャントスルー接続 |

3端子貫通型フィルタ YFF18AC0G106M 1608mm/0603inch, 10uF, 4V x3 pcs シャントスルー接続 |

|---|---|---|---|

| DC/DCコンバータ仕様 入力電圧:5V 出力電圧:1.8V SW周波数:2MHz 出力電流:2A | |||

| 配線イメージ | |||

| 回路図イメージ | |||

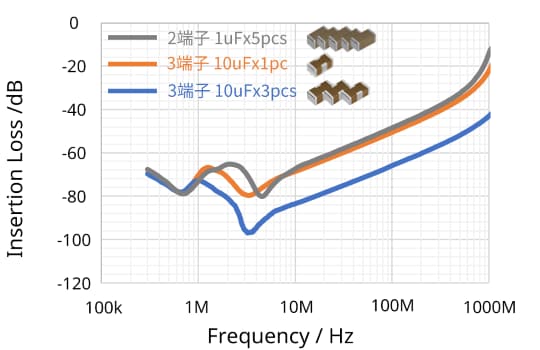

挿入損失比較

2端子

1uFx5pcs

-48.4dB

3端子

10uFx1pc

-50.5dB

3端子

10uFx3pcs

-65.9dB

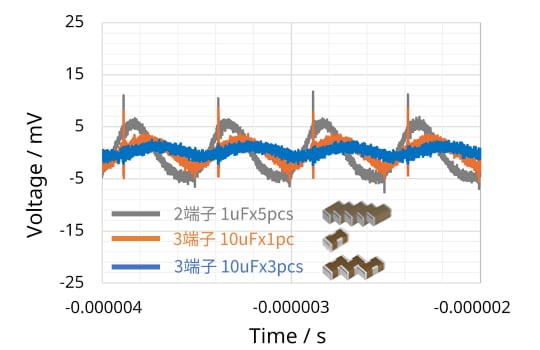

電圧波形比較

2端子

1uFx5pcs

19mVpp

3端子

10uFx1pc

15mVpp

3端子

10uFx3pcs

5mVpp

3端子は高い減衰効果を得ることができ、員数減と特性改善に効果的です。

3端子を複数並列させることにより、高い減衰効果が得られます。

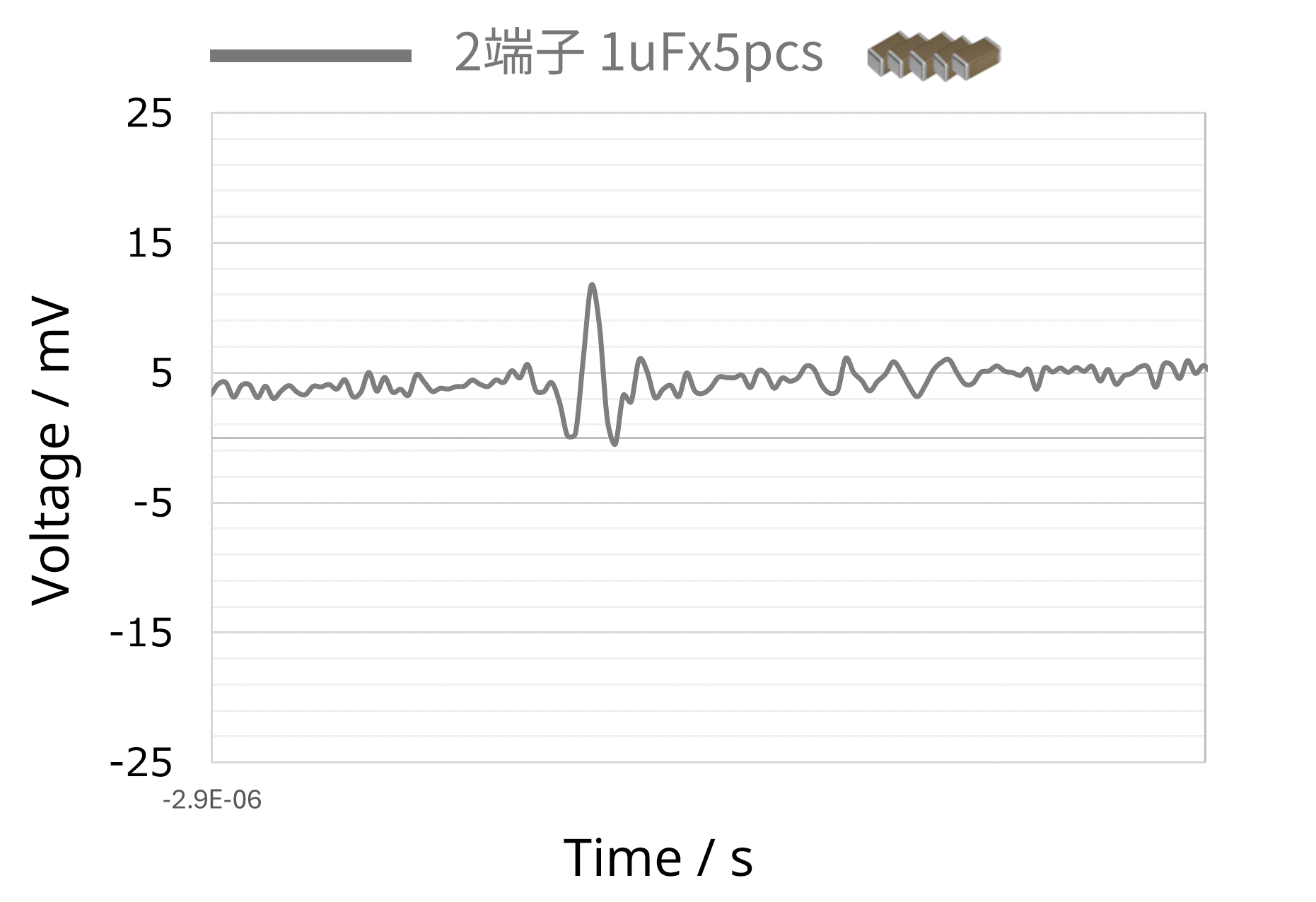

電圧波形をスイッチングノイズにフォーカスしました。

3端子貫通型フィルタの並列数を1個→3個に増やすことによりスイッチングノイズはほぼ除去する事ができました。

電圧波形比較

TDKの大容量3端子貫通型フィルタを搭載する事により、振幅レベルの抑制ができ、員数減への効果が期待されます。

また、3端子の並列数を増やすことにより、並列効果によってより高い減衰効果を得れます。

本事例では3端子を3並列させた構成3において高周波スイッチングノイズがほぼ除去できました。

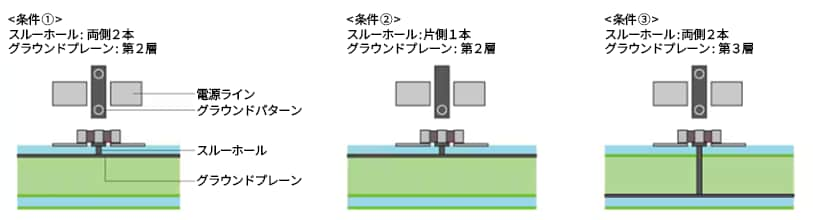

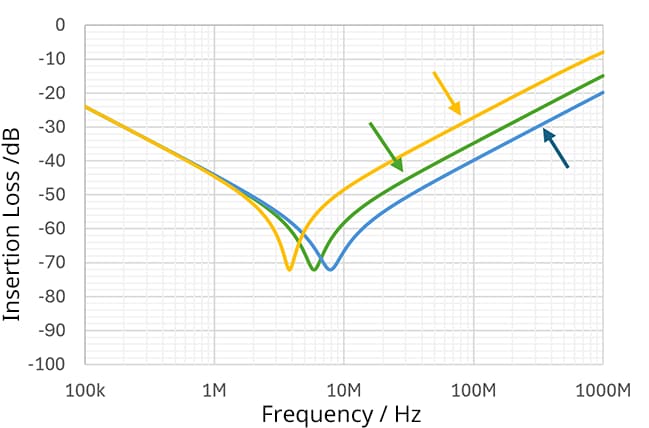

3端子貫通型フィルタの特性を十分に活かすための注意点

3端子貫通型フィルタは単品として低ESLを特徴としていますが、その特徴を十分に引き出すためにはグラウンドパターンやスルーホールによる寄生成分を減らす事が重要です。

図15にグラウンドパターンとグラウンドプレーンを結ぶスルーホールの長さ(深さ)と3端子貫通型フィルタの減衰-周波数特性の関係性を示します。

以下に示す条件①~③の実装条件をシミュレーションにて比較しました。

スルーホールがグラウンドパターンの両端2本の場合(条件①)と片側1本の場合(条件②)では、両側2本の方が大きな減衰量を示します。またともにスルーホールが両側2本でスルーホールの長さが深い(条件③)場合は、スルーホールが短い(浅い)条件①の方が大きな減衰量を示します。

3端子貫通型フィルタ YFF15AC0J105M (1005mm(0402inch) / 6.3V /1uF)

条件 ① 条件 ② 条件 ③3端子貫通型フィルタの特性を十分に引き出すためには、グラウンド端子のスルーホールを多く、スルーホールの長さ(深さ)を短くすることを推奨します。

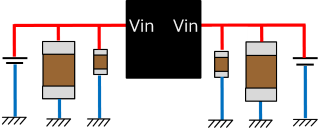

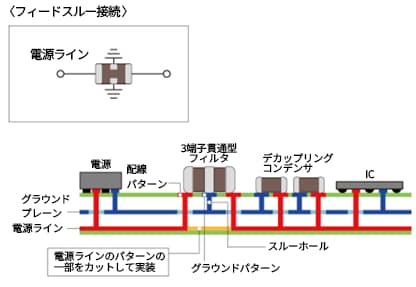

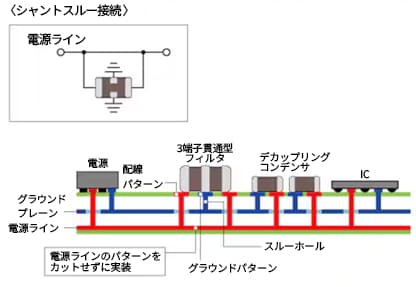

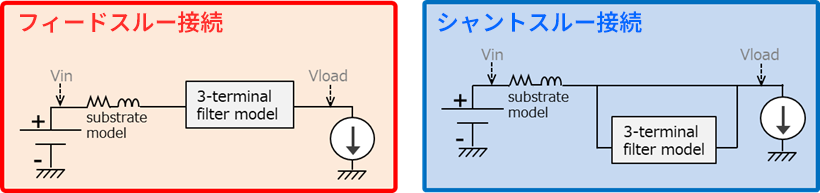

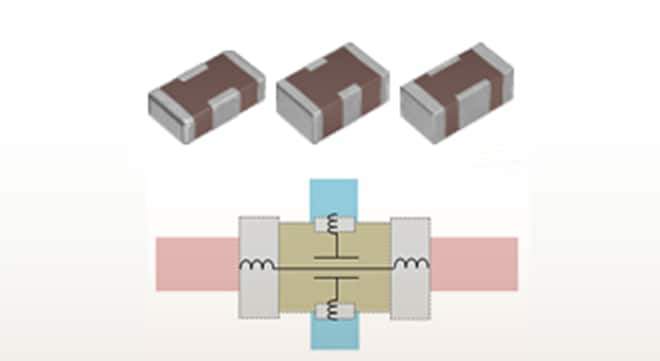

接続方法について

3端子貫通型フィルタは通常電源ラインに接続して使いますが、接続方法が2種類あります。

2種類とは図16に示す通り、電源ラインに対して直列接続であるフィードスルー接続と並列接続であるシャントスルー接続になります。

下図にそれぞれの接続例を示します。本例では多層プリント基板の内層1層目をグラウンドプレーン層、内層2層目を電源ライン層とし、設置にはスルーホールを経由して各プレーンに接続しています。フィードスルー接続については、電源ラインのパターンの一部をカットし実装、シャントスルー接続については電源ラインのパターンはカットせず実装します。

それぞれの接続方法において特徴と主な用途をまとめた表をご確認ください。

| フィードスルー接続 | シャントスルー接続 | |

|---|---|---|

| 実装方法 | ノイズを除去したいラインのパターンの一部をカットして その間に挿入する。 |

ラインの配線パターンをカットせずに、 並列(シャント)接続で実装する。 |

| 主な用途 | 高周波帯域のノイズ除去 (フィルタ用途) |

ICの電圧変動抑制 (デカップリング用途) |

| メリット | 高周波までの広い帯域でノイズ除去効果が高い。 | チップ内を電流がほとんど流れないため、 定格電流の制限がない。 配線パターンをカットしていないので、 基板設計後も員数の変更が容易。 |

| デメリット | チップ内を電流が流れるため、定格電流の制限がある。 電源ライン/信号ラインをカットするため 設計変更が難しい。 |

ESLがフィールドスルー接続とくらべてわずかに高くなる。 |

| ノイズ除去効果 | ◎ | 〇 |

| ライン上のノイズは必ずチップ内を通るので 効果的にノイズをグラウンドに逃がすことができる。 |

一部のノイズは電源ラインを通過してしまうため、 ノイズ除去効果はフィールドスルー接続よりも劣る。 |

|

| 電圧変動抑制効果 | △ (電圧降下が起きる) |

◎ (電圧降下が小さい) |

用途に応じて適切な実装方法を選択してください。

フィードスルー接続では電圧降下がシャントスルー接続より大きくなりますが、ノイズ除去効果は高くなります。またシャントスルーは電源ラインの電圧降下を抑制でき、低電圧回路でもご使用いただけます。上記比較表を参考に、用途にあった接続方法をご選択ください。

まとめ

3端子貫通型フィルタ YFFシリーズは低ESLを特徴としており、ノイズ除去効果が高いことからフィルタ用途、デカップリング用途において、員数減や特性改善への期待から需要が増加しています。TDKでは幅広い定格電圧、静電容量の製品ラインアップがあるため、電源の入力側~出力側までトータルでの製品提案が可能です。一方で今回ご紹介した通り、基板のパターンや接続方法によっても特性が変化します。製品のご使用に関してサポートが必要な場合やPIシミュレーションにご興味があるお客様はぜひTDKへお声がけください。