Q.

ESD対策コンデンサガイド (6): ESD対策に適したコンデンサを選択するにはどのような方法がよいですか。

- コンデンサ(キャパシタ) >

- 積層セラミックチップコンデンサ

A. TDKは実験によって、設計エンジニアがESD対策コンデンサに最適な値を決定する上で役立つ3つの重要なパラメータを定めています。それは(1)破壊電圧、(2)静電容量、(3)DCバイアスです。

-

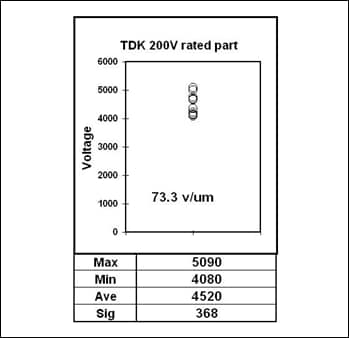

Vbd(Voltage BreakDown、破壊電圧)は、コンデンサの電圧レベル強度を定量化するための試験方法です。部品が壊れるまでDC電圧を固定の昇圧速度(例 100v/s)でコンデンサに印加します。これによってコンデンサが耐えられる最大持続電圧を測定しますが、最大ESD電圧レベルが直接分かるわけではあ りません。

Vbd試験要結果の例 -

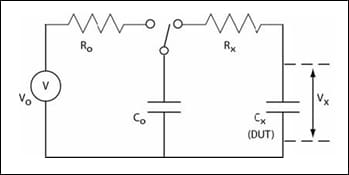

試験試料の静電容量によって、試料にかかる実効電圧が変わります。

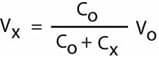

節点分析によると、DUT(Cx)の測定電圧(Vx)の関係は以下のように表されます。

電源電圧(Vo)と充電コンデンサ(Co)を一定に保つと、測定電圧(Vx)とDUTコンデンサ(Cx)は反比例します。つまり、選択するCxの容量が高いほどVxは低下します。

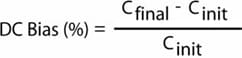

コンデンサによる効果を説明するため、たとえば1000pFコンデンサ(Cx)のESD要件が4kV(Vo)の場合を見てみましょう。また、AEC-Q200試験方法を使用し、Co = 150pFと仮定します。試験試料による効果は、4kVを印加した場合、Cxはわずか521.7V(Vx)となって現れます。 - DC電圧をセラミックコンデンサに印加すると、静電容量の実効値はその公称容量と異なる場合があります。DCバイアスは通常、静電容量の変化率で表されます。

DCバイアスは主に誘電体に起因します。当然、他の設計や構造と言った要因も影響します。C0GのようなClass I誘電体の場合、変化は比較的わずかです。X7RやX5RのようなClass II誘電体の場合、静電容量は微増した後すぐに減少に転じ、DCバイアスはおおよそ-10%~-70%程度です。

印加電圧を上げると実効静電容量は減少します。

>>積層セラミックチップコンデンサ製品サイト

その他製品に関することは弊社担当営業または代理店もしくは本Webサイトよりお問い合わせください。